# RFD3T5N200-703

# SP3T PIN Switch Driver - Positive & Negative Voltage Driver

### **Features:**

- Supports High Output Drive Voltage and Current

- Support RFuW Engineering SP3T High Power Switches

- Operates from +5V and -15V to -200V

- Independent TTL Input Controls

- · Complimentary Driver Outputs

- RoHS Compliant

### **Description:**

The RFD3T5N200-703 surface mount PIN Switch Driver supports high biasing voltages required when operating PIN diodes switches under high power applications. The fundamental building block consists of a PIN Diode and it is the intrinsic layer which gives this device its unique characteristics. When charge is injected into the intrinsic layer it becomes highly conductive and when charge is depleted from the intrinsic layer it becomes nonconductive. As the operating power increase or the frequency of interest drops into the HF & VHF realms, the necessary biasing voltages climb into the hundreds of voltage which exceeds the capabilities of all MMIC style Switch Drivers.

This RFD3T5N200-703 has been designed to support optimum biasing voltages required to support SP3T switches operating at high power and low frequencies. It offers both positive and negative biasing voltages. The RFD3T5N200-703 operates with a positive bias voltage of +5V and a negative voltage between -15V to -200V depending on the application's power handling and frequency of operation.

The RFD3T5N200-703 driver can source up to -100mA from the negative source and up to +50mA from the +5V supply. The driver is controlled via an independent TTL control signals. There are three complimentary outputs to support the typical series-shunt PIN diode switch topology.

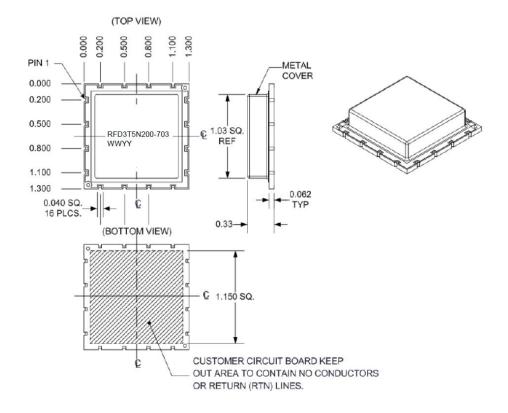

The RFD3T5N200-703 is packaged in a 33mm x 33mm x 8.4mm surface mount package. The device is compatible with surface mount, solder reflow processes typically employed in high volume production.

**Environmental Capabilities**

The RFD3T5N200-703 Driver is capable of meeting the environmental requirements of MIL-STD-202 and MIL-STD-750.

ESD and Moisture Sensitivity Rating

The ESD rating for this device is Class 1A, HBM. The moisture sensitivity level rating is MSL1.

# **Absolute Maximum Ratings**

$T_{A}$ = +25°C as measured on the base ground surface of the device.

| Parameter                              | Conditions                            | Absolute Maximum Value |

|----------------------------------------|---------------------------------------|------------------------|

| Input Voltage, +V <sub>CC</sub>        |                                       | -0.1 to 5.5 V          |

| Input Voltage, -VEE                    |                                       | 0.1 to -210 V          |

| Control Port Input Voltage             |                                       | -0.5 to 5.5 V          |

| -VEE Output Sink Current               | V <sub>OUT</sub> ~ -V <sub>EE</sub> V | -125 mA                |

| +V <sub>CC</sub> Output Source Current | V <sub>OUT</sub> ~ +V <sub>CC</sub> V | +60 mA                 |

| Operating Temperature                  |                                       | -40°C to 85°C          |

| Storage Temperature                    |                                       | -65°C to 150°C         |

| Assembly Temperature                   | T < 10 sec                            | +260°C                 |

| Total Dissipated Power                 | $T_{CASE} = 85^{\circ}C$              | 6.0 W                  |

Note 1:  $T_{\text{CASE}}$  is defined as the temperature of the bottom ground surface of the device.

## **RFD3T5N200-703 Electrical Specifications**

@  $Z_o$ =50 $\Omega$ , TA= +25°C as measured on the base ground surface of the device.

| Parameters                                   | Symbol                                | Test Conditions                                                                                                | Min<br>Value           | Typ<br>Value             | Max<br>Value           | Units |

|----------------------------------------------|---------------------------------------|----------------------------------------------------------------------------------------------------------------|------------------------|--------------------------|------------------------|-------|

| Operating Frequency                          | PRF                                   |                                                                                                                | 0                      | 100                      | 500                    | KHz   |

| Supply Voltage                               | +Vcc                                  |                                                                                                                | 4.5                    | 5                        | 5.5                    | V     |

| Supply Voltage                               | -VEE                                  |                                                                                                                | -15                    | -50                      | -200                   | dB/°C |

| Quiescent Current (+Vcc)                     | I <sub>Q1</sub>                       | +V <sub>CC</sub> =5V, -V <sub>EE</sub> =-15V to -200V,<br>No load connected to output A & B                    | 10                     | 20                       | 30                     | mA    |

| Quiescent Current (=V <sub>EE</sub> )        | I <sub>Q2</sub>                       | +V <sub>CC</sub> =5V, -V <sub>EE</sub> =-15V to -200V,<br>No load connected to output A & B                    | -15                    | -25                      | -40                    | mA    |

| TTL Input Voltage                            | V <sub>LOW</sub><br>V <sub>HIGH</sub> | Logic 0<br>Logic 1                                                                                             | 0<br>2                 |                          | 0.8<br>5.0             | V     |

| Low Level Output Voltage<br>Output A, B or C | Voutl                                 | +Vcc=5V, -VEE=-15V to -200V,<br>Source current from +Vcc=50mA                                                  | +Vcc<br>-1             | +Vcc<br>-0.5             | +Vcc<br>-0.1           | V     |

| Low Level Output Voltage<br>Output A, B or C | V <sub>оитн</sub>                     | +V <sub>CC</sub> =5V, -V <sub>EE</sub> =-15V to -200V,<br>Sink current from -V <sub>EE</sub> = 50mA            | -V <sub>EE</sub><br>+1 | -V <sub>EE</sub><br>+0.5 | -V <sub>EE</sub><br>-1 | V     |

| Switching Time                               | Tsw                                   | +V <sub>CC</sub> =5V, -V <sub>EE</sub> =-15V to -200V,<br>F =10kHz, 50% TTL to 10% or 90%<br>RF output voltage |                        | 1.5                      | 2                      | usec  |

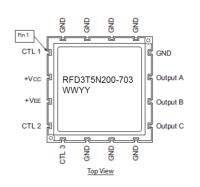

### RFD3T5N200-703 Pin Out

# **Pin Out Description**

| Pin | Pin Name         | Input/Output | Description                                       |

|-----|------------------|--------------|---------------------------------------------------|

| 1   | CTL1             | I            | TTL input control (CTL1)                          |

| 2   | +V <sub>CC</sub> |              | +5V supply voltage input                          |

| 3   | -V <sub>EE</sub> |              | Negative high voltage (-15 to -200V) input        |

| 4   | CTL2             |              | TTL input control 2 (CTL2)                        |

| 5   | CTL3             |              | TTL input control 3 (CTL3)                        |

| 6   | GND              |              | +V <sub>CC</sub> & -V <sub>EE</sub> ground return |

| 7   | GND              |              | +V <sub>CC</sub> & -V <sub>EE</sub> ground return |

| 8   | GND              |              | +V <sub>CC</sub> & -V <sub>EE</sub> ground return |

| 9   | Output C         | 0            | Bias voltage/current output from driver port C    |

| 10  | Output B         | 0            | Bias voltage/current output from driver port B    |

| 11  | Output A         | 0            | Bias voltage/current output from driver port A    |

| 12  | GND              |              | +V <sub>CC</sub> & -V <sub>EE</sub> ground return |

| 13  | GND              |              | +V <sub>CC</sub> & -V <sub>EE</sub> ground return |

| 14  | GND              |              | +Vcc & -Vee ground return                         |

| 15  | GND              |              | +Vcc & -Vee ground return                         |

| 16  | GND              |              | +Vcc & -Vee ground return                         |

### **Truth Table**

| CTL1<br>(notes 1 & 2) | CTL2<br>(notes 1 & 2) | CTL3<br>(notes 1 & 2) | Driver Output<br>Section A                                     | Driver Output<br>Section B                                     | Driver Output<br>Section C                                     |

|-----------------------|-----------------------|-----------------------|----------------------------------------------------------------|----------------------------------------------------------------|----------------------------------------------------------------|

| VHIGH                 | V <sub>LOW</sub>      | V <sub>LOW</sub>      | V <sub>OUT</sub> =+V <sub>CC</sub> V,<br>current sourcing mode | V <sub>OUT</sub> ~ -V <sub>EE</sub> V,<br>Current sinking mode | V <sub>OUT</sub> ~ -V <sub>EE</sub> V,<br>Current sinking mode |

| V <sub>LOW</sub>      | VHIGH                 | VHIGH                 | V <sub>OUT</sub> ~ -V <sub>EE</sub> V,<br>Current sinking mode | V <sub>OUT</sub> =+V <sub>CC</sub> V,<br>current sourcing mode | V <sub>OUT</sub> =+V <sub>CC</sub> V,<br>current sourcing mode |

| V <sub>HIGH</sub>     | $V_{LOW}$             | V <sub>HIGH</sub>     | V <sub>OUT</sub> =+V <sub>CC</sub> V,<br>current sourcing mode | V <sub>OUT</sub> ~ -V <sub>EE</sub> V,<br>Current sinking mode | V <sub>OUT</sub> =+V <sub>CC</sub> V,<br>current sourcing mode |

| $V_{LOW}$             | V <sub>HIGH</sub>     | $V_{LOW}$             | V <sub>OUT</sub> ~ -V <sub>EE</sub> V,<br>Current sinking mode | V <sub>OUT</sub> =+V <sub>CC</sub> V,<br>current sourcing mode | V <sub>OUT</sub> ~ -V <sub>EE</sub> V,<br>Current sinking mode |

| VHIGH                 | VHIGH                 | $V_{LOW}$             | V <sub>OUT</sub> =+V <sub>CC</sub> V,<br>current sourcing mode | V <sub>OUT</sub> =+V <sub>CC</sub> V,<br>current sourcing mode | V <sub>OUT</sub> ~ -V <sub>EE</sub> V,<br>Current sinking mode |

| V <sub>LOW</sub>      | V <sub>LOW</sub>      | VHIGH                 | V <sub>OUT</sub> ~ -V <sub>EE</sub> V,<br>Current sinking mode | V <sub>OUT</sub> ~ -V <sub>EE</sub> V,<br>Current sinking mode | V <sub>OUT</sub> =+V <sub>CC</sub> V,<br>current sourcing mode |

| V <sub>LOW</sub>      | $V_{LOW}$             | $V_{LOW}$             | Note 3                                                         | Note 3                                                         | Note 3                                                         |

| VHIGH                 | VHIGH                 | VHIGH                 | Note 3                                                         | Note 3                                                         | Note 3                                                         |

Notes:

- 1)  $2V \le VHIGH \le 5V$

- 2) 0V ≤ VLOW ≤ 0.8V

- 3) Not recommended state

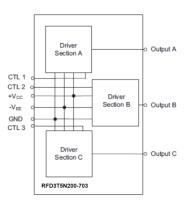

# **Control of Symmetrical SP3T Switch**

The RFD3T5N200-703 can control a symmetrical SP3T series-shunt PIN Diode switch. Each driver section is connected to one series-shunt switch element to provide biasing voltages required in the two operating states: RF State 1 and 0. The RF State of the SP3T is determined by the inputs to the three Control signals: CTL1, CTL2 & CTL3. Each Control signal states drives the SP3T into a state where one port is in the Low Loss state while the other two ports are in the Isolation state.

| CTL1 | CTL2 | CTL3 | RF<br>State | Path<br>J0 to<br>J1 | Path<br>J0 to<br>J2 | Path J0<br>to J3  | Output A<br>J1 Bias                                                                          | Output B<br>J2 Bias                                                                          | Output C<br>J3 Bias                                                                          |

|------|------|------|-------------|---------------------|---------------------|-------------------|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| LOW  | HIGH | HIGH | 1           | Low<br>Loss         | High<br>Isolation   | High<br>Isolation | V <sub>OUT</sub> ~ -V <sub>EE</sub> ,<br>Current sink<br>mode                                | V <sub>OUT</sub> ~(+V <sub>CC</sub> –<br>I <sub>OUT</sub> x 191)V,<br>current source<br>mode | V <sub>OUT</sub> × 191)V,<br>current source<br>mode                                          |

| HIGH | LOW  | HIGH | 2           | High<br>Isolation   | Low<br>Loss         | High<br>Isolation | V <sub>OUT</sub> ~(+V <sub>CC</sub> –<br>I <sub>OUT</sub> x 191)V,<br>current source<br>mode | V <sub>OUT</sub> ~ -V <sub>EE</sub> ,<br>Current sink<br>mode                                | V <sub>OUT</sub> ~(+V <sub>CC</sub> –<br>I <sub>OUT</sub> x 191)V,<br>current source<br>mode |

| HIGH | HIGH | LOW  | 3           | High<br>Isolation   | High<br>Isolation   | Low<br>Loss       | V <sub>OUT</sub> ~(+V <sub>CC</sub> –<br>I <sub>OUT</sub> x 191)V,<br>current source<br>mode | V <sub>OUT</sub> ~(+V <sub>CC</sub> –<br>I <sub>OUT</sub> x 191)V,<br>current source<br>mode | V <sub>OUT</sub> ~ -V <sub>EE</sub> ,<br>Current sink<br>mode                                |

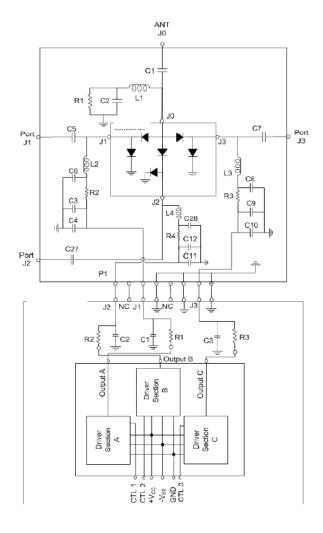

### **Positive & Negative Voltage PIN Diode Switch Driver**

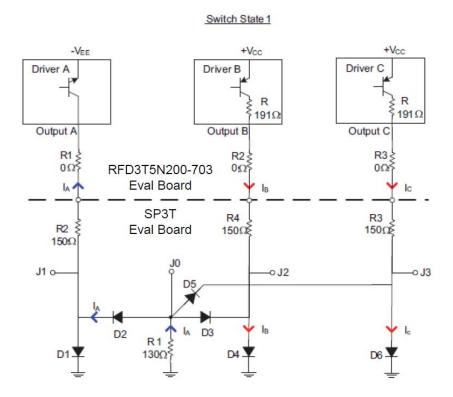

#### RF State 1

The schematic shown below reflect RF State 1 for the RFD3T5N200-703 driver interconnected to a SP3T evaluation board.

In RF State 1, the voltage from Output A of Driver A is approximately equal to  $-V_{EE}$  supply voltage. This provides a forward bias to the series PIN diode, D2, between the J0 and J1 ports. The magnitude of the resultant bias current through D2 is primarily determined by the output voltage from Output A, the magnitude of the forward voltage across D2 and the sum of the resistance of R1 and R2 on the SP3T evaluation board and R1 on the driver evaluation board. This current is nominally -100 mA.

At the same time, the PIN diodes D4, D6 connected between J2 and ground, J3 and ground are also forward biased by the voltage produced at Output B of Driver B, Output C of Driver C. The voltages are slightly less than  $+V_{CC}$  due to the voltage drop across the  $191\Omega$  internal resistors. Under this condition, the PIN diodes, D3, D5 connected between the J0, J2 and J0, J3 ports are reverse biased. The magnitude of the bias currents through D4 is primarily determined by  $+V_{CC}$ , the magnitude of the forward voltage across D4 and the sum of the resistanceof R4 on the switch eval board, R2 on the driver eval board and the  $191\Omega$  internal resistor. Similarly, the bias currents through D6 is determined by  $+V_{CC}$ , the magnitude of the forward voltage across D6 and the sum of the resistances of R3 on the switch eval board, R3 on the driver eval board and the  $191\Omega$  internal resistor. Nominally current through each shunt diode D4 and D6 is 15mA.

The series PIN diodes, D3, D5 must be reverse biased during RF State 1. The reverse bias voltage must be sufficiently large to maintain this diode in its non-conducting, high impedance state when a large RF signal voltage may be present in the J0 to J1 path. The reverse voltage across D3 is the arithmetic difference of the

potentials at its anode and cathode, similarly reverse voltage across D5 is the arithmetic of the potentials at its anode and cathode.

The potential at D3's cathode is equal to the forward voltage of D4 and the potential at D5's cathode is equal to the forward voltage of D6. These voltages are nominally 0.8V. The potential at D3's anode is equal to the voltage drop across R1 of the SP3T eval board. This voltage is the product of the current through D2 and the resistance of R1. The voltage across D3 is given by:

```

V_{D3} = V_{ANODE\ D3} - V_{CATHODE\ D3} = V_{ANODE\ D3} - 0.8 V_{ANODE\ D3} = I_A\ x\ R1 = \left[ (-V_{EE} + VD2)/(R1 + R2) \right] x\ R1 \sim \left[ (-28 + 0.8)/280 \right] x\ 130 = -12.6V V_{D3} = V_{ANODE\ D3} - V_{CATHODE\ D3} = -12.6 - 0.8 = -13.4V

```

The potential at D5 anode can also be calculated as above. The anode of D5 potential will be equal to the potential of the anode of D3.

The minimum voltage required to keep D3 and D5 out of conduction is a function of the magnitude of the RF voltage present, the standing wave present at the D3 and D5 anodes, the frequency of the RF signal and the characteristics of the seriesdiode, among other factors. The minimum required voltage can be calculated as described in the section "Minimum Reverse Bias Voltage".

#### RF State 2

The simplified DC Bias circuit schematic for RF State 2 for the RFD3T5N200-703 driver interconnect to the SP3T eval board is shown below.

In RF State 2, the voltage from Output B of Driver B is approximately equal to the  $-V_{EE}$  supply voltage. This provides a forward bias to the series PIN diode, D3, between the J0 and J2 ports. The magnitude of the resultant bias current through D3 is primarily determined by the output voltage from Output B, the magnitude of the forward voltage across D3 and the sum of the resistances of R1 and R4 on the SP3T eval board and R2 on the driver eval board. Under this condition, the series diodes D2 and D5 are reversed biased.

The magnitude of the bias current through D1 is primarily determined by  $+V_{CC}$ , the magnitude of the forward voltage across D1 and the sum of the resistances of R2 on the switch eval board, R1 on the driver eval board and the internal  $191\Omega$  resistor. Similarly, the magnitude of the bias current through D6 is primarily determined by +VCC, the magnitude of the forward voltage across D6 and the sum of the resistances of R3 on the switch eval board, R3 on the driver eval board and the internal  $191\Omega$  resistor. The nominal currents through each of these shunt diodes is 15mA.

The series PIN diodes, D2 and D5 must be reversed biased during RF State 2. The reverse bias voltage must be sufficiently large to maintain this diode in its non-conducting, high impedance state when a large RF signal voltage may be present in the J0 to J2 path. The reverse voltage across D2 and the diode D5 is the arithmetic difference of the potentials at their anode and cathode terminals.

#### Switch State 2

The potential at D2's cathode is equal to the forward voltage of D1 and the potential at D5's cathode is equal to the forward voltage of D6. This voltage is nominally 0.8V. The potential at D2's anode is equal to the voltage drop across R1 of the SP3T eval board. The voltage is the product of the current through D3 and the resistance of R1. The voltage across D2 is given by the following:

$$V_{D2} = V_{ANODE\ D2} - V_{CATHODE\ D3} = V_{ANODE\ D2} - 0.8$$

$$V_{ANODE\ D2} = I_B\ x\ R1 = \left[ (-V_{EE} + V_{D3})/(R1 + R2) \right] x\ R1 \sim \left[ (-28 + 0.8)/280 \right] x\ 130 = -12.6 V_{D2}$$

$$V_{D2} = V_{ANODE\ D2} - V_{CATHODE\ D2} = -12.6 - 0.8 = -13.4 V_{D2}$$

Similarly, the voltage across D5 can be calculated and the value would be equal to -13.4V.

The minimum voltage required to keep the diodes D2 & D5 out of conduction is a function of the magnitude of the RF voltage present, the standing wave present at anodes of D2 and D5, the frequency of the RF signal and the characteristics of the series diodes, among other factors. The minimum required voltage can be calculated as described in the section "Minimum Reverse Bias Voltage".

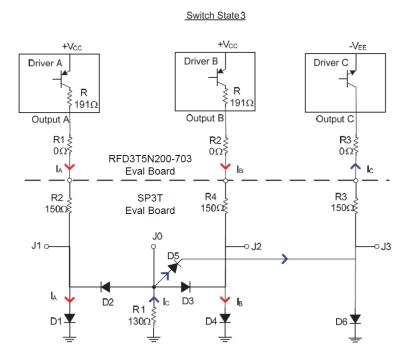

#### RF State 3

The simplified DC bias circuit schematic for RF State 3 for the RFD3T5N200-703 driver interconnected to the SP3T eval board is shown below.

In RF State 3, the voltage from Output C of Driver C is approximately equal to the  $-V_{EE}$  supply voltage. This provides a forward bias to the series PIN diodes, D5, between the J0 to J3 ports. The magnitude of the resultant bias current through D5 is primarily determined by the output voltage from Output C, the magnitude of the forward voltage across D5 and the sum of the resistances of R1 and R3 on the SP3T eval board and R2 on the driver eval board. This current is nominally -100mA.

At the same time, the PIN diodes, D1 and D4 connected between J1, ground and J2 and ground are also forward biased by the voltage produced at output A of Driver A, Output B of Driver B respectively. The driver output voltages are a bit less than  $+V_{CC}$  due to the voltage drop across the  $191\Omega$  internal resistor. Under this condition the series diodes D2 and D5 are both reversed biased.

The magnitude of the bias current through D1 is primarily determined by  $+V_{CC}$ , the magnitude of the forward voltage across D1 and the sum of the resistance of R2 on the switch eval board, R1 on the driver eval board and the internal  $191\Omega$  resistor. Similarly, the magnitude of the bias current through D4 is determined by  $+V_{CC}$ , the magnitude of the forward voltage across D4 and the sum of the resistances of R4 on the SP3T eval board, R2 on the driver eval board and the internal  $191\Omega$  resistor. The nominal currents through each of these shunt diodes is 15mA.

The series PIN didoes, D2 and D3 must be reversed biased during RF State 3. The reverse bias voltage must be sufficiently large to maintain this diode in its non-conducting, high impedance state when a large RF signal voltage may be present in the J0 to J3 path. The reverse voltage across D2 and the diode D3 is the arithmetic difference of the potentials at their anode and cathode terminals. The potential at D2's cathode is equal to the voltage of D1 and the potential at D3's cathode is equal to the forward voltage of D4. The voltage is nominally 0.8V.

The potential at D2's anode is equal to the voltage drop across R1 of the SP3T eval board. This voltage is the product of the current through D3 and the resistance of R1. The voltage across D2 is determined by the following:

$$V_{D2} = V_{ANODE\ D2} - V_{CATHODE\ D3} = V_{ANODE\ D2} - 0.8$$

$$V_{ANODE\ D2} = I_B\ x\ R1 = \left[ (-V_{EE} + V_{D3})/(R1 + R2) \right] x\ R1 \sim \left[ (-28 + 0.8)/280 \right] x\ 130 = -12.6 V$$

$$V_{D2} = V_{ANODE\ D2} - V_{CATHODE\ D2} = -12.6 - 0.8 = -13.4 V$$

Similarly, the voltage across the D3 can be calculated, and the value would beequal to -13.4V.

The minimum voltage required to keep the diodes D2 and D3 out of conduction is a function of the magnitude of the RF voltage present, the standing wave present at the anode terminals of diodes D2 and D3, the frequency of the RF signal and the characteristic of the series diode, among other factors. The minimum required voltage can be calculated as described in the section "Minimum Reverse Bias Voltage".

#### **Calculation of Resistor Values**

The magnitude of the forward bias current applied to the series diode is set by the magnitude of the supply voltage –VEE, which is nominally 28V, the value of resistors R1 and R2 or R3 on the SP3T eval board as well as R1 on the driver eval board, the forward of the series diode, VDIODE, among other factors. Given the desired currentvalue, the resistance is given by the following formula:

RTOTAL = R 1 or 2(driver board) + R 2 or 3 (SP3T eval board) +  $191\Omega = (+V_{CC} - V_{DIODE})/I_{BIAS}$

### Minimum Reverse Bias Voltage

$$|V_{DC}| = \frac{|V_{RF}|}{\sqrt{1 + \left[\left(\frac{0.0142 \times f_{MHZ} \times W_{mils}^2}{V_{RF} \times \sqrt{D}}\right) \times \left(1 + \sqrt{1 + \left(\frac{0.056 \times V_{RF} \times \sqrt{D}}{W_{mils}}\right)^2}\right)\right]^2}}$$

The minimum reverse bias voltage required to maintain a PIN diode out of conduction in the presence of a large RF signal given by the following variables:

| V<sub>DC</sub>| = magnitude of the minimum DC reverse bias voltage

| V<sub>RF</sub>| = magnitude of the peak RF voltage(including the effects of VSWR)

$f_{MHz}$  = lowest RF signal frequency expressed in MHz

D = duty factor of the RF signal

W<sub>mils</sub> = I region thickness of the PIN Diode (expressed in mils)

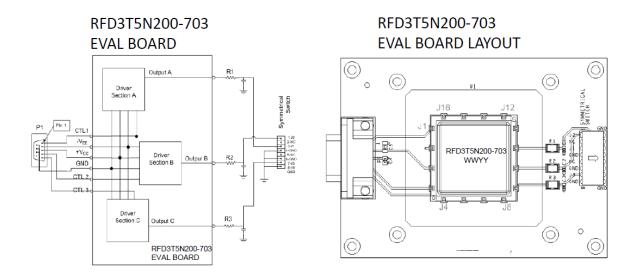

The RFD3T5N200-703 eval board contains several passive components. R1 and C1 are optional components which may be used to shape the output signal of Output A. Likewise, R2 and C2, R3 and C3 may be used to shape the output signal from Output B, Output C respectively. C1, C2 and C3 capacitors are normally not installed. R1, R2 and R3 are installed with  $0\Omega$ , 0.5W resistors. The positive supply voltage, nominally 5V, is designated as +Vcc. The negative supply voltage, nominally -15V to -200V, is designated as -Vee.

There are two multi-pin connectors on the board. P1 is a DB-9 male connector which facilitates connection of the TTL control signal, supply voltages and ground to the eval board. Symmetrical switch is a 16 pin female header which can be used to connect directly to the male header on the symmetrical SP3T Eval Board. The pin out for these connectors are shown below:

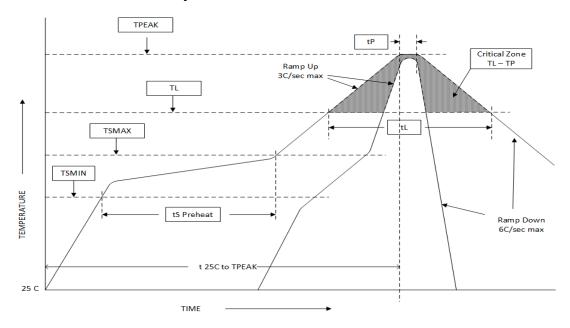

### **Assembly Instructions**

The RFD3T5N200-703 may be attached to the printed circuit card using solder reflow procedures using either RoHS or Sn63/ Pb37 type solders per the Table and Temperature Profile Graph shown below:

| Profile Parameter                                        | Sn-Pb Assembly Technique | RoHS Assembly Technique |

|----------------------------------------------------------|--------------------------|-------------------------|

| Average ramp-up rate (T <sub>L</sub> to T <sub>P</sub> ) | 3°C/sec (max)            | 3°C/sec (max)           |

| Preheat                                                  |                          |                         |

| Temp Min (T <sub>smin</sub> )                            | 100°C                    | 100°C                   |

| Temp Max (T <sub>smax</sub> )                            | 150°C                    | 150°C                   |

| Time ( min to max) (t <sub>s</sub> )                     | 60 – 120 sec             | 60 – 180 sec            |

| T <sub>smax</sub> to T <sub>L</sub>                      |                          |                         |

| Ramp up Rate                                             |                          | 3°C/sec (max)           |

| Peak Temp (T <sub>P</sub> )                              | 225°C +0°C / -5°C        | 260°C +0°C / -5°C       |

| Time within 5°C of Actual Peak<br>Temp (T <sub>P</sub> ) | 10 to 30 sec             | 20 to 40 sec            |

| Time Maintained Above:                                   |                          |                         |

| Temp (T <sub>L</sub> )                                   | 183°C                    | 217°C                   |

| Time (t <sub>L</sub> )                                   | 60 to 150 sec            | 60 to 150 sec           |

| Ramp Down Rate                                           | 6°C/sec (max)            | 6°C/sec (max)           |

| Time 25°C to T <sub>P</sub>                              | 6 minutes (max)          | 8 minutes (max)         |

# **Solder Re-Flow Time-Temperature Profile**

# RFD3T5N200-703 Package Outline Drawing

#### Notes:

- 1) Circuit Board material is FR4.

- 2) Metallization: 2 0z Cu followed by 150uin (TYP), followed by 4uin (TYP) Au

- 3) Unit = inches

# **Part Number Ordering Detail:**

The RFD3T5N200-703 PIN Switch Driver is available in the following format:

| Part Number        | Description                                    | Packaging |

|--------------------|------------------------------------------------|-----------|

| RFD3T5N200-703     | SP3T Positive & Negative Voltage Switch Driver | Tube      |

| RFD3T5N200-703-EVB | RFD3T5N200-703 Evaluation Board                | Box       |